Xilinx FPGA器件结构

Xilinx fpga的组成

xilinx fpga 主要由IOBs 和CLBs 组成

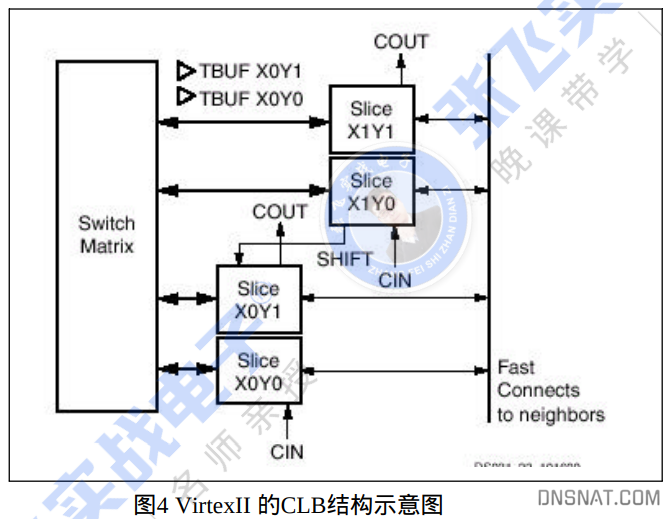

CLB

CLB含有4个相似的Slice

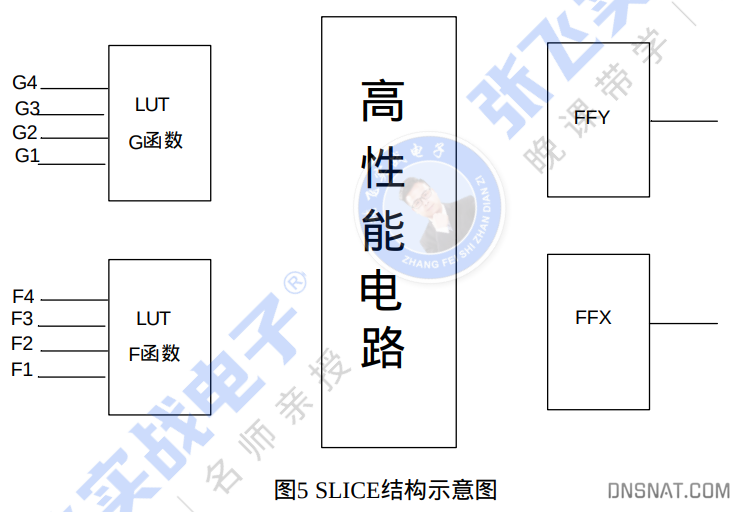

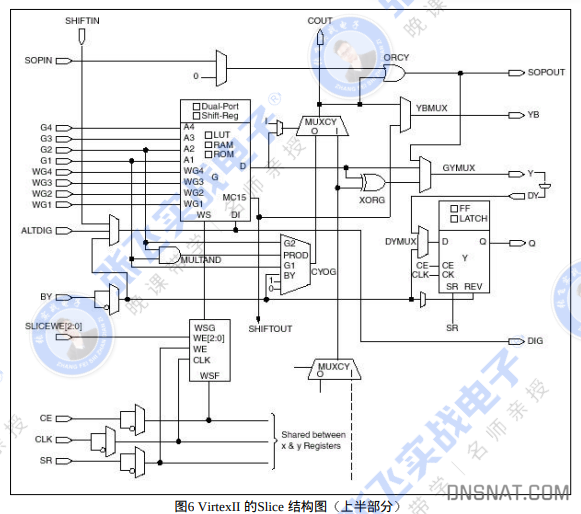

Slice

Slice基本元件包括 2个4输入LUT G函数 F函数 2个Storage element FFX FFY一般用做D触发器

LUT

LUT本身是一个16X1的RAM结构 它的4个输入 G函数 G1 G4 F函数 F1 F4 其实是RAM的地址线 通过对RAM中各存储单元进行配置 可灵活配置成任意1 4输入任意组合逻辑或者直接用它作RAM或ROM 这本身就是它原来的特点。

Slice(LUT、FF、LATCH)的概念

6系列之前的器件中都有Latch;6系列和7系列的FPGA 中,一个Slice中有50%的storage element可以被配置为Latch或者Flip-Flop

LUT(look up table):

查找表本质是一个RAM,将数据事先存储在其中。当输入一个信号后,根据信号所指向的地址进行查表,找出地址对应的内容进行输出。

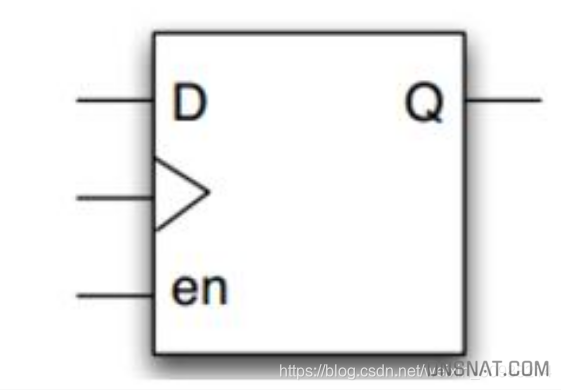

FF(Flip Flop):

触发器,时钟沿触发,可以存储1bit的数据,是reg的基本存储单位。

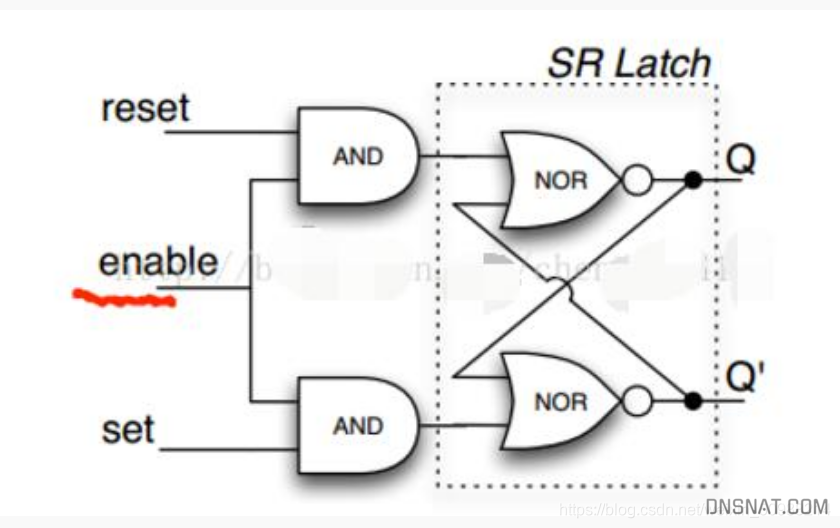

结构图如下:

DFF:D类触发器,是边沿触发,属于时序逻辑。(reg就是由DFF组成,一个8位寄存器,用了8个同步的D触发器)

FF的优点:

1、边沿触发,同步设计,不容易受到毛刺的影响。

2、时序分析简单。

缺点:

1、面积比latch大(锁存器==>寄存器)

LATCH:

一种锁存器。电平触发,非同步控制。在使能信号有效时,LATCH相当于通路(en=1,则 output =input);使能信号无效时,LATCH保存不变。(en=0,则output(当前)=output(之前))

Latch优点:

1、面积比ff小:门电路时构成组合逻辑电路的基础,锁存器和寄存器是时序逻辑电路的基础。构成顺序:晶体管==>门电路==>锁存器==>触发器。

2、latch锁存器速度比ff触发器速度快。

缺点:

1、电平触发,非同步设计,受到布线延迟影响大,容易导致输出产生毛刺

clk

fpga clk线路为黄金线路,到各个器件延迟基本相同、时间抖动也很小。

vivado verilog简单逻辑